I2C (Inter IC) wurde in den 1980er von Philips (jetzt NXP) entwickelt.

Es ist ein serieller Datenbus und sollte - wie im Namen bezeichnet - eine interne

Kommunikation zwischen einzelnen ICs herstellen. Daher war der Bus auch

nur für geringe Leitungslängen ausgelegt.

I2C ist Multi-Master/Multi-Slave fähig. Für die Kommunikation zwischen den einzelnen Devices werden lediglich zwei Signalleitungen SCL (serial clock) und SDA (serial data) benötigt (wobei der elektrische Rückpfad immer GND ist). Anfänglich lag die Datenrate bei 100kbit/s. Mit dem 7bit Adressraum konnten 128-16 = 112 Devices auf dem Bus kommunizieren (16 Adressen b'0000xxx' und b'1111xxx' sind hierbei reserviert).

In weiteren Versionen der Spezifikation wurde der Adressraum auf 10bit erweitert. Dadurch konnten nochmals 1024 zusätzliche Devices und somit insgesamt 1136 Devices angesprochen werden. Neben des Adressraums wurde auch noch die Datenrate gesteigert. Hier wurden in der Version V1.0 der "fast mode" mit 400kbit/s, in der Version V2.0 der "high speed mode" oder HS-mode mit 3,4Mbit/s und dann in der Version V4.0 auch der "ultra fast mode" mit 5Mbit/s (jedoch nur noch unidirektional) definiert.

I2C ist Multi-Master/Multi-Slave fähig. Für die Kommunikation zwischen den einzelnen Devices werden lediglich zwei Signalleitungen SCL (serial clock) und SDA (serial data) benötigt (wobei der elektrische Rückpfad immer GND ist). Anfänglich lag die Datenrate bei 100kbit/s. Mit dem 7bit Adressraum konnten 128-16 = 112 Devices auf dem Bus kommunizieren (16 Adressen b'0000xxx' und b'1111xxx' sind hierbei reserviert).

In weiteren Versionen der Spezifikation wurde der Adressraum auf 10bit erweitert. Dadurch konnten nochmals 1024 zusätzliche Devices und somit insgesamt 1136 Devices angesprochen werden. Neben des Adressraums wurde auch noch die Datenrate gesteigert. Hier wurden in der Version V1.0 der "fast mode" mit 400kbit/s, in der Version V2.0 der "high speed mode" oder HS-mode mit 3,4Mbit/s und dann in der Version V4.0 auch der "ultra fast mode" mit 5Mbit/s (jedoch nur noch unidirektional) definiert.

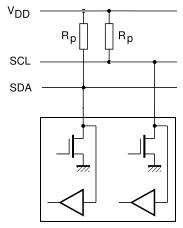

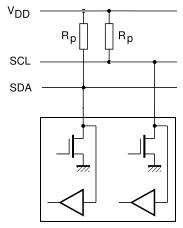

Physikalische Anbindung:

Die Treiberbausteine der Busleitungen SCL und SDA sind in jedem Gerät

laut Spezifikation als open Drain ausgeführt. Demnach muss der Bus

über PullUp Widerstände Rp im Ruhezustand (Idle Mode) auf

jeweils H-Potenzial liegen.

Die tatsächlich mögliche Anzahl von Devices am Bus ist jedoch

von der sich damit ergebenden Buskapazität Cb in Verbindung mit

den gewählten PullUp Widerständen und der gewünschten Datenrate abhängig!

Bei der Auslegung des Busses müssen die technischen Spezifikation der einzelnen Devices bekannt sein. Hier spielt vor allem die maximale Spannungsversorgung der Knoten eine wichtige Rolle. In der Vergangenheit waren VDD=5V die Regel, mittlerweile wird VDD=3V3 bevorzugt. Nun dürfen diese Devices - ohne Eingriff - nur dann am gleichen Bus hängen, wenn vor allem die VDD=3V3 Geräte auch 5V tolerant sind. Andernfalls muss der Bus in einen 5V und einen 3V3 Bereich unterteilt werden und beide Bereiche anschliessend über einen Levelshifter angekoppelt werden. Anders verhält es sich bei der Nutzung von 7bit bzw. 10bit adressierbaren Devices. Diese dürfen immer am gleichen Bus angeschlossen werden.

Bei der Auslegung des Busses müssen die technischen Spezifikation der einzelnen Devices bekannt sein. Hier spielt vor allem die maximale Spannungsversorgung der Knoten eine wichtige Rolle. In der Vergangenheit waren VDD=5V die Regel, mittlerweile wird VDD=3V3 bevorzugt. Nun dürfen diese Devices - ohne Eingriff - nur dann am gleichen Bus hängen, wenn vor allem die VDD=3V3 Geräte auch 5V tolerant sind. Andernfalls muss der Bus in einen 5V und einen 3V3 Bereich unterteilt werden und beide Bereiche anschliessend über einen Levelshifter angekoppelt werden. Anders verhält es sich bei der Nutzung von 7bit bzw. 10bit adressierbaren Devices. Diese dürfen immer am gleichen Bus angeschlossen werden.

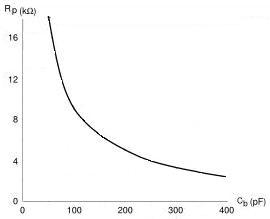

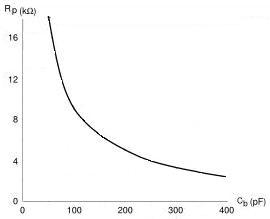

PullUp Widerstände:

Um einen I2C Bus zu betreiben werden auf beiden Leitungen SCL und SDA

an mindestens einer Stelle im System PullUp Widerstände benötigt.

Die richtige Dimensionierung hängt jedoch von mehreren Faktoren

ab. Hier gibt es zunächst einen unteren Wert Rpmin, der so

berechnet wird, dass sich ein maximaler Strom von 3mA nach GND ergibt.

Dies wurde von Philips so festgelegt.

Rpmax = tr / (0.85 x Cb)

- bei VDD=5V ergibt sich für Rpmin somit ein Wert von 1.66kΩ.

- bei VDD=3V3 ergibt sich für Rpmin somit ein Wert von 1kΩ.

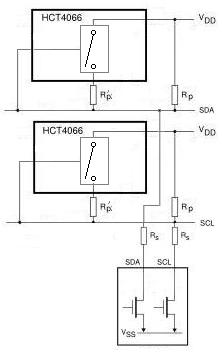

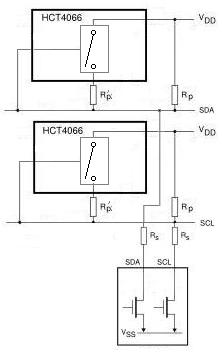

Schaltbare PullUp Widerstände:

Dieses Verfahren ist optional dafür vorgesehen die geforderte Flankensteilheit

bei der gegebenen Buskapazität und dem minimalen Rp einzuhalten. Für den

Fall, dass Rp bereits den minimalen Wert (sodass 3mA nach GND abgeleitet

werden können) aufweist, kann z.B. mittels Analogschalter HCT4066 ein

weiterer Rp' parallel zum eigentlichen PullUp Widerstand Rp

geschaltet werden. Der Einsatz eines schaltbaren PullUp Widerstands ist jedoch

erst bei HS-mode Bussen vorzusehen.

Rp' wird nur dann aktiviert wenn es zu einem L-H Übergang kommt bzw.

sobald der Schaltpegel des Analogschalters von 2.0V überschritten wird.

Rp' wird so berechnet, dass dann die Flankensteilheit tr

(80ns bis 1µs) eingehalten wird. Die Parallelschaltung bleibt dann solange

aktiv, bis es wieder zu einem H-L Übergang kommt bzw. sobald der Schaltpegel

des Analogschalters von 0.8V unterschritten wird. Während dieser kurzen

Zeitspanne kann dann evtl. der Maximalstrom von 3mA überschritten werden.

Der Übergangswiderstand der Analogschalter selbst kann mit ca. 70Ω

vernachlässigt werden.

Rpx = Rp || Rp'

Rpx = tr / (-ln(0.7) x Cb)

=> Rp' = Rp / ((Rp/Rpx)-1)

Rpx = tr / (-ln(0.7) x Cb)

=> Rp' = Rp / ((Rp/Rpx)-1)

Serienwiderstände:

Diese können optional vor jedes Device und in jede Leitung eingefügt

werden. Sie sollen einerseits vor Spikes schützen und können eine

gegenseitige Einkoppelung von Störsignalen reduzieren. Serienwiderstände

liegen hierbei in einer Größenordnung von ca. 100Ω. Der

Wert von Rs beeinflußt jedoch auch die Berechnung von

Rp mit Rpx = Rp + Rs.

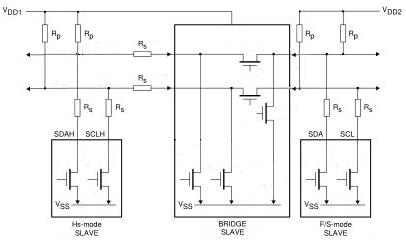

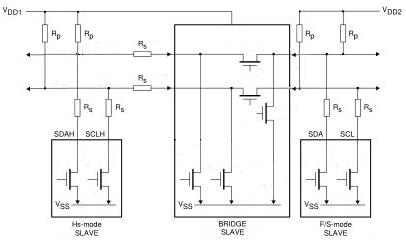

I2C-Bridge:

Die I2C Bridge ist immer dann notwendig, wenn Devices mit unterschiedlichen

Datenraten am selben Bus betrieben werden. Gerade dann, wenn mindestens

ein HS-Device und ein Standard/Fast Mode Device zum Einsatz kommt, trennt

die Bridge den Bus in einen HS-Teil und einen Standard/FS-Teil auf.

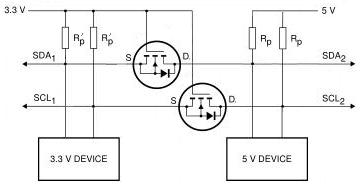

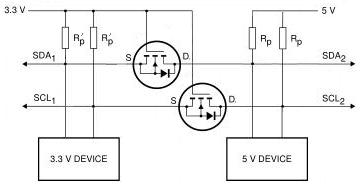

Mit einem Levelshifter können Devices mit unterschiedlichen Betriebsspannungen

am selben Bus betrieben werden. Der Levelshifter besteht aus einem N-Kanal

MOSFET mit integrierter Body-Diode (enhancement type), der in beide Leitungen

SCL und SDA integriert wird. Sollte der MOSFET keine interne Diode besitzen,

so muss diese als Schottkydiode extern verdrahtet werden. Die Gates müssen an

die jeweils niedrigste Versorgungsspannung angeschlossen sein. Ein geeigneter

MOSFET ist z.B. der BSS138. Es ist zu beachten, dass auf beiden Seiten des

MOSFETs jeweils eine PullUp Widerstandsgruppe Rp' und Rp

vorhanden sein muss. Beide Widerstandsgruppen müssen für die jeweilige

VDD ausgelegt sein.

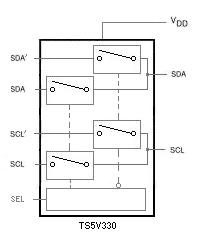

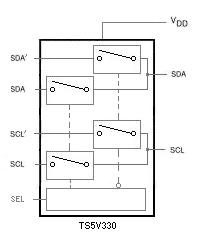

Für den Fall, dass unterschiedliche SLAVES mit nicht veränderbaren Adressen

am gleichen Bus betrieben werden sollen oder müssen, kann der Bus in zwei

oder mehrere einzelne Segmente unterteilt werden. Hierzu kann z.B. der

dargestellte Baustein verwendet werden. Im Bild wurde absichtlich auf die

notwendigen Pull-Up Widerstände verzichtet, da diese ohnehin vorhanden sein

müssen. Auch hier gilt dann wieder: Es ist zu beachten, dass auf beiden Seiten des

Multiplexers jeweils eine PullUp Widerstandsgruppe Rp' und Rp

vorhanden sein muss. Andernfalls kann der inaktive Zweig Fehlfunktionen aufweisen.

Dies soll auch eine Fehlfunktion im Umschaltmoment verhindern. Beide

Widerstandsgruppen müssen für die jeweilige VDD ausgelegt sein.

Kabelanordung / Layout:

Sobald die Leitungslängen von SCL bzw. SDA über 10cm hinausgehen, bedarf es

einer bestimmten Anordnung bzw. Kabelführung der Signalleitungen. Bei einem

dreiadrigen Kabel oder bei einem zweilagigen Layout ist die Anordnung:

SCL,GND,SDA. Existiert in einem mehrlagigen Layout eine eigene GND plane,

können die Signalleitungen nebeneinander geroutet werden. Bei

einem vieradrigen Kabel ist die Anordnung: SCL,VDD,GND,SDA.

Kommen Twisted-Pair-Kabel zum Einsatz, muss SCL und SDA jeweils mit GND

als Rückpfad verdrillt sein und VDD einzeln geführt werden.

Alternativ kann SCL mit VDD und SDA mit GND verdrillt werden.

In diesem Fall müssen jedoch an beiden Enden der Leitung Blockkondensatoren

zwischen VDD und GND angebracht sein. Bei geschirmten Kabeln

muss der Schirm auf GND liegen.

Protokollaufbau:

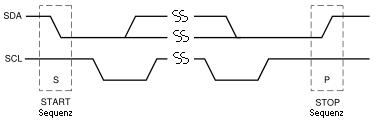

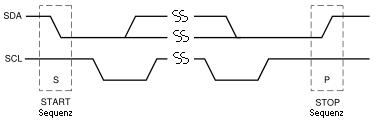

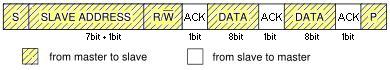

Nur ein Master-Device kann die Kommunikation einleiten. Hierzu wird

ein Takt auf SCL generiert. Die normale Datenübertragung beginnt mit

einer START-Sequenz (S) und endet mit einer STOP-Sequenz (P). Dazwischen

liegen 8bit lange Adress- und Datenbytes.

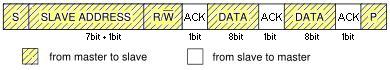

Nach jedem gesendeten Byte erfolgt vom angesprochenen SLAVE-Device im 9. Bit eine

Quittierung ACK (⇒ SDA=L). Bleibt diese aus nACK (⇒ SDA=H), muss

der MASTER die Kommunikation mit STOP abbrechen oder mit einem weiteren START

neu aufsetzen. Daher ist im Allgemeinen das erste vom MASTER gesendete Byte

ein Adressbyte des Empfängers. Alle weiteren Bytes im Protokoll werden dann

vom jeweiligen Hersteller des SLAVE-Devices spezifiziert.

Eine leere Sequenz, nur aus START und STOP bestehend, ist nicht erlaubt.

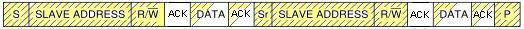

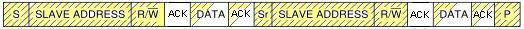

Eine verkettete Datenübertragung endet vorerst nicht mit einem STOP, sondern setzt eine weitere Kommunikation unvermittelt mit einer wiederholten START-Sequenz (Sr) anstatt einer STOP-Sequenz fort. Dies kann beliebig lange ausgeführt werden, bis schliesslich die gesamte Übertragung mit einem STOP beendet wird.

Eine verkettete Datenübertragung endet vorerst nicht mit einem STOP, sondern setzt eine weitere Kommunikation unvermittelt mit einer wiederholten START-Sequenz (Sr) anstatt einer STOP-Sequenz fort. Dies kann beliebig lange ausgeführt werden, bis schliesslich die gesamte Übertragung mit einem STOP beendet wird.

Adressierungsformat:

I2C kennt zwei unterschiedliche Adressierungsarten. In der ursprünglichen

Version gab es zunächst nur die 7bit Adressierung. Diese wurde bereits

mit der Spezifikation V1.0 auf 10bit erweitert. Seither kann man beide

Arten, auch gleichzeitig am selben Bus, benutzen.

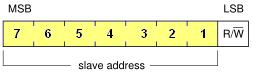

- 7bit Adressierung:

Der MASTER sendet nur ein Adressbyte und nur der SLAVE mit exakt dieser Adresse generiert ein ACK. Eine SLAVE-Adresse wird in den Datenblättern der Hersteller sehr oft als 8bit Wert angegeben. So bedeutet eine 0xA0 im übertragenen Sinn b'1010000x', wobei Bit 0 (LSB) eine Sonderrolle zukommt.

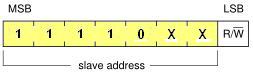

- 10bit Adressierung:

Um bei einem Mischbetrieb (7bit, 10bit Adressierung) am Bus eindeutig zu signalisieren, ob der MASTER einen 7bit oder einen 10bit SLAVE ansprechen wird, bedient er sich einer der 16 reservierten Adressen - nämlich der b'11110xx'. Für alle 7bit SLAVES ist diese Adresse reserviert, alle 10bit SLAVES warten bei Übereinstimmung ihrer obersten beiden Adressbits auf das nächste Byte. Weiterhin generieren in dieser Übertragungsphase ALLE Slaves, deren Adresse im ersten Adressbyte übereinstimmen gleichzeitig ein ACK. Anschliessend sendet der MASTER ein weiteres Adressbyte um somit einen eindeutig definierten SLAVE anzusprechen. Jetzt wird nur noch dieser SLAVE ein ACK produzieren.

- Adressierung im HS-Mode:

Eine Besonderheit muss beachtet werden, sobald Devices im HS-Mode betrieben und vom MASTER angesprochen werden sollen. Hierzu wird eine reservierte Adresse - nämlich die b'00001xxx' ausgegeben. Dieser MASTER-Code identifiziert einen von bis zu 8 MASTER-Devices, von dem aus die Übertragung initiiert wird. Da es sich hierbei noch nicht um eine SLAVE-Adresse handelt, wird KEIN Device dieses Byte quittieren. Diese Sequenz muss im Standard/Fast-Mode ausgeführt werden. Erst danach darf die höhere Datenrate vom MASTER ausgegeben und SLAVE-Devices mit einer 7bit oder einer 10bit Adresse angesprochen werden. Sobald die Datenübertragung mit STOP beendet wird, schalten alle Devices wieder zurück zum Standard/Fast-Mode.

Clock-Stretching:

Jedes SLAVE-Device kann zu jedem Zeitpunkt die Übertragung vom MASTER

blockieren um z.B. interne Abläufe zu synchronisieren. Hierzu hält

das Device in einer SCL-L-Phase den Clock seinerseits auf L. Damit

kann der MASTER keine weiteren Impulse mehr auf der SCL-Leitung

ausgeben - die Übertragung stoppt (Es gibt z.B. Hersteller von Sensoren, die

den Bus für ca. 1s blockieren, bis die interne Wandlung abgeschlossen ist).

Um dieses Verfahren zu erkennen, muss der MASTER mit jeder Ausgabe eines

H-Pegles auf der SCL Leitung diesen auch zurücklesen und prüfen. Hat der

MASTER seinen eigenen H-Pegel erkannt, darf er das nächste Bit übertragen.

Datasampling:

Die SLAVE-Devices lesen im allgemeinen den Datenpegel mit einer

steigenden SCL-Flanke ein. Dies gilt nicht für eine START/STOP Erkennung.

Erfolgt diese Erkennung nicht automatisch innerhalb der SLAVES (z.B. bei

Einsatz eines Devices ohne integrierte I2C-Peripherie bzw. bei

Implementierung einer Software I2C), muss der Datenpegel zyklisch während

der SCL-H-Phase ausgewertet werden. Der MASTER darf die Übertragung zu

jeder Zeit, auch während einer unvollständigen Datenausgabe, mit einem

STOP oder einem repeated START abbrechen. Im letzteren Fall müssen alle

SLAVES ihre interne Bus-Logik zurücksetzen und im nächsten Byte eine

Adresse erwarten.

Die Buskapazität kann im laufenden Betrieb mit Hilfe eines Oszilloskops

indirekt ausgemessen werden. Hierzu werden die SCL und SDA Leitungen

hochauflösend aufgezeichnet und dann die Flankensteilheit der steigenden

Flanken beurteilt. Diese Flanken bilden in Verbindung mit den bekannten

PullUp Widerstandswerten Rp und der unbekannten Buskapazität

Cb eine e-Funktion. Um Cb zu ermitteln, wird die

Zeit t=Τ im Bereich von USCL = {0;0.63VDD} bzw.

USDA = {0;0.63VDD} gemessen und daraus ergibt sich

Cb = Τ / Rp.

Dann nehmen Sie gleich Kontakt mit uns auf oder informieren Sie sich über unser Entwicklungsangebot